## RapidRF LDMOS Front-End Designs

## **RAPIDRF-FRONTEND**

Last Updated: Dec 8, 2023

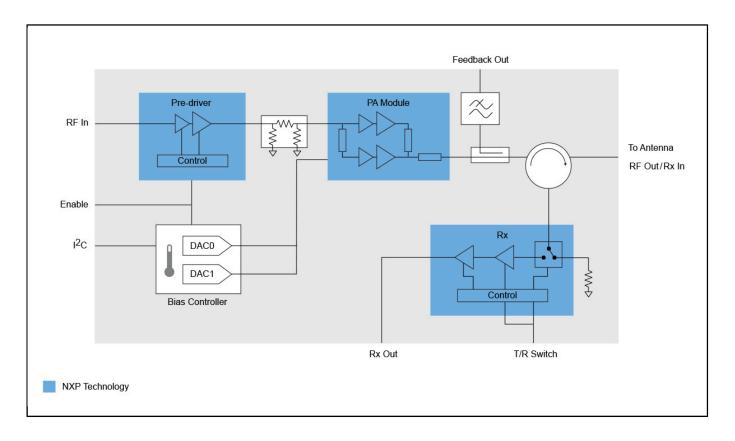

NXP's RapidRF front-end designs for 5G infrastructure integrate a linear pre-driver, RF power amplifier, Rx LNA with T/R switch, a circulator and a bias controller in a compact footprint. They incorporate a coupler for DPD feedback and are to be used with digital pre-distortion.

RapidRF reference boards are ideal for 5G radio units requiring 2.5 to 5 Watts (34-37 dBm) average transmit power at the antenna. Versions for different bands use a common PCB layout, simplifying both design and manufacturing for faster time-to-market.

## RapidRF Front-end Block Diagram Block Diagram

View additional information for RapidRF LDMOS Front-End Designs.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.