# AN12533

# Add Criterion for Valid User Code into HEX file

Rev. 0 — 07/09/2019 Application Note

### 1 Introduction

When developing LPC800 parts in MDK, and LPC8N04 part in MCUXpresso, customer may face a problem. After compilation, the HEX file may not contain the Criterion for Valid User Code, It may result in the user code burned into chips cannot be executed.

The Criterion for Valid User Code is used to judge whether the user code is valid or invalid. The reserved CPU exception vector location 7 (offset 0x0000 001C in the vector table) should contain the 2's complement of the checksum of table entries 0 through 6. It causes the checksum of the first 8 table entries to be 0.

During startup, the bootloader code calculates checksum for the first 8 locations in sector 0 of the flash. If the checksum is not zero; indicating valid user code is not found, the bootloader enters USART ISP mode automatically while do not execute the code from address 0x0.

If developing LPC800 parts using IAR, after compiling, the Criterion for Valid User Code will be added into HEX file automatically.

While using MDK and MCUXpresso, after compiling, the Criterion for Valid User Code will not be added into HEX file automatically, it is needed to do something manually to add the criteria.

Below methods introduce how to add Criterion for Valid User Code into HEX file automatically during compile procedure under MDK and MCUXpresso.

## 2 Solutions to add Criterion for Valid User Code into HEX file

### 2.1 Under MDK

There are two solutions to add the Criterion for Valid User Code during MDK compile procedure.

#### 2.1.1 Solution1

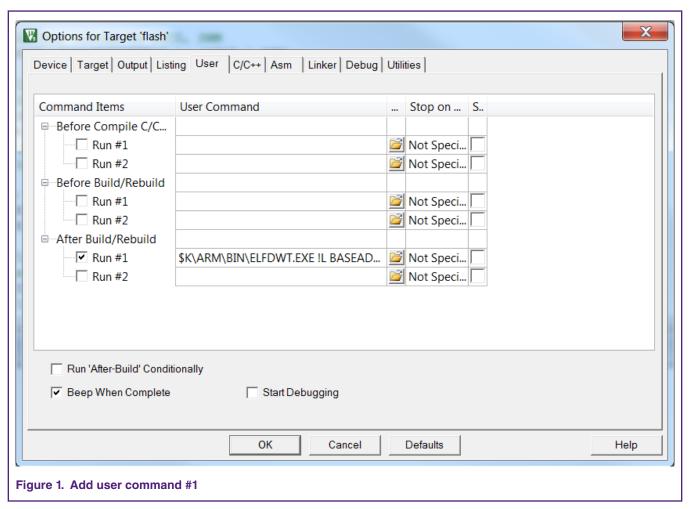

Enter "Options for target" setting interface, click "User" tab,

Add user command #1: \$K\ARM\BIN\ELFDWT.EXE !L BASEADDRESS(0x00000000)

See Figure 1:

The Criterion for valid user code is shown in Figure 2:

```

Build Output

compiling system.c...

assembling Keil startup.s...

compiling i2c.c...

compiling gpio.c...

compiling swm.c...

compiling Keil_Retarget.c...

compiling utilities.c...

compiling syscon.c...

linking...

Program Size: Code=3404 RO-data=264 RW-data=52 ZI-data=708

After Build - User command #1: C:\MDK526\\ARM\BIN\ELFDWT.EXE .\Objects\I2C Master.axf BASEADDRESS(0x00000000)

ELFDWT - Signature Creator V1.4.0.0

COPYRIGHT Copyright (C) 2014-2018, ARM Ldt. and ARM Germany GmbH

*** Updated Signature over Range[32] (0x00000000 - 0x00000018): 0x0000001C = 0xEFFFF87F

*** Processing completed, no Errors.

".\Objects\I2C Master.axf" - 0 Error(s), 0 Warning(s).

Build Time Elapsed: 00:00:03

Figure 2. Get the Criterion for valid user code

```

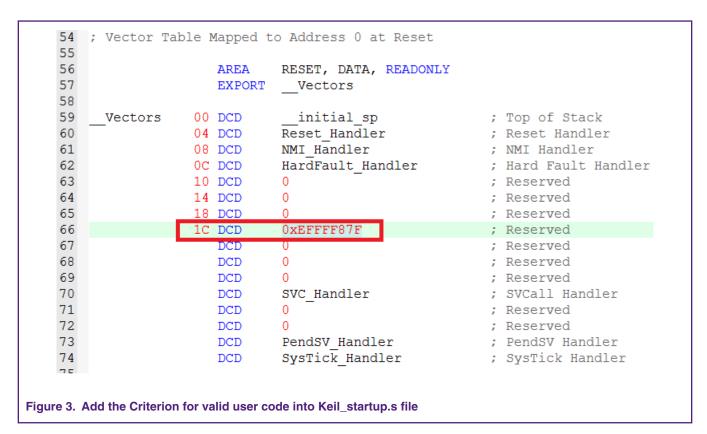

When get the Criterion for valid user code, add it into Keil\_startup.s file, at offset 0x0000 001C in the vector table as Figure 3.

#### 2.1.2 Solution2

Another solution to put the Criterion for Valid User Code into HEX file is running user command totally.

First, add user command #1:

\$K\ARM\BIN\ELFDWT.EXE !L BASEADDRESS(0x00000000)

Second, add user command #2:

\$K\ARM\ARMCC\BIN\fromelf.exe --i32 --output=xxx.hex .\Objects\xxx.axf

#### NOTE

Solution2 works for NXP LPC800 Code Bundle MDK. For NXP LPC800 SDK MDK, SDK uses different compiling config, the solution2 cannot be used, only the solution1 can work.

# 2.2 Under MCUXpresso

MCUXpresso IDE provides an API, named: \_\_valid\_user\_code\_checksum

User is required to add this API into Keil\_startup.s file, at offset 0x0000 001C in the vector table. Then, the Criterion for Valid User Code is added into HEX file after compilation.

Application Note 3/5

```

//

// The vector table.

// This relies on the linker script to place at correct location in memory.

extern void (* const g_pfnVectors[])(void);

__attribute__ ((used, section(".isr_vector")))

void (* const g_pfnVectors[])(void) = {

// Core Level - CMOplus

& vStackTop, // The initial stack pointer

ResetISR.

// The reset handler

NMI Handler,

// The NMI handler

HardFault_Handler,

// The hard fault handler

0,

// Reserved

0,

// Reserved

// Reserved

valid user code checksum,

// LPC MCU Checksum

0,

// Reserved

0,

// Reserved

0,

// Reserved

SVC Handler,

// SVCall handler

// Reserved

0,

// Reserved

0,

PendSV Handler,

// The PendSV handler

// The SysTick handler

SysTick_Handler,

Figure 4. Add the Criterion for valid user code into Keil startup.s file

```

For those LPC800 parts with available SDK code, the API is already added at 0x1C.

For LPC8N04, without available SDK code, maybe user uses different version code to do development. And for LPC8N04, the chip has different silicon versions with different bootloader, special attention is required to the vector checksum verification.

There are two bootloader versions (version 0.12 and version 0.14) available for the LPC8N04. The difference between the two Boot ROM versions is that version 0.14 supports application vector checksum verification before booting the image while version 0.12 does not support.

If the code for bootloader version 0.12 is used directly for bootloader version 0.14 chips, the vector checksum verification missing issue maybe happened. User need check whether the API exists on 0x1C in the vector table. If not, need add the API manually to 0x1C. The code for bootloader version 0.14 do not have this issue.

# 3 Revision history

**Table 1. Revision history**

| Revision history |          |                 |

|------------------|----------|-----------------|

| Rev              | Date     | Description     |

| 0                | 20190709 | Initial release |

Add Criterion for Valid User Code into HEX file, Rev. 0, 07/09/2019

Application Note 4 / 5

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFIRE, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET. TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, UMEMS, EdgeScale, EdgeLock, eIQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, μVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2019.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 07/09/2019

Document identifier: AN12533