High-Performance Quad-Core DSP with Security

The MSC8154E device is one of Our fourth-generation high-end multicore DSP devices that target broadband wireless base stations and other communications infrastructure with security processing. The MSC8154E is a four-core DSP based on NXP’s SC3850 StarCore® technology and designed to advance the capabilities of wireless broadband equipment. It delivers higher performance and power savings, leveraging 45 nm process technology in a highly integrated system-on-chip (SoC) to provide performance equivalent to a 4 GHz single-core device. The MSC8154E helps equipment manufacturers and carriers create solutions and services that enable near-term, mainstream adoption of next-generation wireless standards such as 3G-LTE, WiMAX, HSPA+ and TDD-LTE. The device is designed to lower system costs by integrating functionality into a single device that previously required multiple discrete parts.

The MSC8154E DSP delivers a high level of performance and integration, combining four fully programmable new and enhanced SC3850 DSP cores, each running at up to 1 GHz with an architecture highly optimized for wireless infrastructure applications. Developed by NXP® and integrated on-chip, the MAPLE-B baseband accelerator supports hardware acceleration for Turbo and Viterbi channel decoding and for DFT/iDFT and FFT/iFFT algorithms and includes CRC processing. An internal RISC-based QUICC Engine® subsystem supports multiple networking protocols to guarantee reliable data transport over packet networks while significantly offloading processing from the DSP cores.

The MSC8154E embeds large internal memory and supports a variety of advanced, high-speed interface types, including two RapidIO® interfaces, two gigabit Ethernet interfaces for network communications, a PCI Express® controller, two DDR controllers for high-speed, industry standard memory interface, four multi-channel TDM interfaces and a security encryption/decryption processor (SEC).

製品詳細

Features

- Four StarCore® DSP SC3850 core subsystems operating at up to 1 GHz/8000 MMACS per core and up to 32000 MMACS per device

- Multi accelerator platform engine for baseband (MAPLE-B)

- High-speed, high-bandwidth CLASS fabric arbitrates between the DSP cores and other CLASS leaders to M2 memory, M3 memory, DDR controllers, MAPLE-B and the configuration registers

- Two DDR controllers with up to 400 MHz clock (800 MHz data) rate and 32/64-bit DDR2/3 SDRAM data bus

- Dual RISC core QUICC Engine® subsystem operating at up to 500 MHz provides parallel packet processing independent of the DSP cores

- HSSI that supports two 4x SerDes ports

- Security engine core (SEC) optimized to process all the cryptographic algorithms associated with IPSec, IKE, SSL/TLS, 3GPP and LTE

- Four TDM interfaces

- UART and I²C interfaces

- Eight software watchdog timers

- Sixteen 16-bit timers, two 32-bit general purpose timers per core for RTOS support

- I/O interrupt concentrator and virtual interrupt support, eight hardware semaphores

- Thirty-two GPIO ports multiplexed with interface signals and IRQ inputs

- Boot options: Ethernet, Serial RapidIO, I²C and serial peripheral interface (SPI)

- Three input clocks and five PLLs

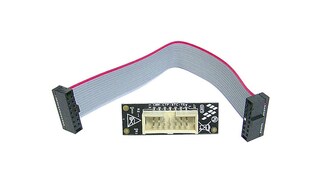

- JTAG Test Access Port (TAP) and boundary scan architecture designed to comply with IEEE® Std. 1149.1 profiling and performance monitoring support

- Reduced power dissipation with wait, stop and power down low-power standby modes

- Optimized power management circuitry

- CMOS 45 nm SOI technology in 29 mm x 29 mm, 783 ball FC-PBGA package

ドキュメント

クイック・リファレンス ドキュメンテーションの種類.

1-5 の 54 ドキュメント

-

セレクタ・ガイド

DSP Product Summary Brochure注目

-

ファクト・シート

MSC8154 Broadband Wireless Access DSP注目

-

製品概要

MSC8154E Product Brief注目

-

ファクト・シート

MSC8154 ADS Fact Sheet注目

設計・リソース

ソフトウェア

エンジニアリング・サービス

NXPから直接サポートを受けるには、以下のサイトをご覧ください。 エンジニアリング・サービス.

3 エンジニアリング・サービス

-

インディペンデントデザインハウス (IDH)

ハードウェア/ソフトウェア・エンジニアリング・サービス

-

インディペンデントデザインハウス (IDH)

Embedded firmware consulting

-

インディペンデントデザインハウス (IDH)

Hardware Engineering Services

本製品をサポートするパートナーの一覧は、 パートナーマーケットプレイス.

.jpg?imwidth=300)